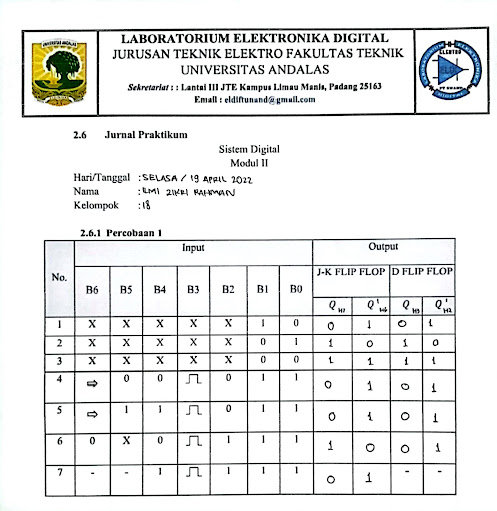

Percobaan 1

1. Jurnal (DAFTAR ISI)

2. Alat dan Bahan (DAFTAR ISI)

a. Module D’Lorenzo

b. Jumper

3. Rangkaian Simulasi (DAFTAR ISI)

4. Prinsip Kerja Rangkaian (DAFTAR ISI)

Untuk percobaan 1 ini menngunakan Module D’Lorenzo panel DL 2203S. Pada

rangkaian terdapat J-K Flip Flop dan D Flip Flop.

Pada rangkain J-K Flip Flop, B0 dihubungkan ke input Reset, B1

dihubungkan ke input Set, B2 dihubungkan ke input J, B3 dihubungkan ke CLOCK, B4

dihubungkan ke input K. Lalu, keluaran Q dihubungkan ke H7 dan keluaran Q’dihubungkan

ke H6.

Pada rangkaian D Flip Flop, B0 dihubungkan ke input Reset, B1

dihubungkan ke input Set, B5 dihubungkan ke input D, dan B6 dihubungkan ke

CLOCK. Lalu, keluaran Q dihubungkan ke H3 dan keluaran Q’dihubungkan ke H2.

Atur logika pada relay B0-B6 sesuai perintah pada table percobaan maka

akan didapatkan data pada jurnal.

5. Video Rangkaian (DAFTAR ISI)

6. Analisa (DAFTAR ISI)

1) Bagaimana jika B0 dan B1 sama sama diberi logika 0,

apa yang terjadi pada rangkaian?

Pada rangkaian, B0 dihubungkan ke input Reset dan B1 dihubungkan ke input Set. Jika B0 dan B1 sama-sama diberi logika 0, maka arus akan mengalir dari ground menuju input Set dan Reset. Hal ini membuat Set dan Reset akan aktif (ACTIVE LOW) sehingga J-K tidak berpengaruh lagi. Jadi pada rangkaian terjadi kondisi Terlarang.

2) Bagaimana jika B3 diputuskan/tidak dibubungkan pada

rangkaian apa yang terjadi pada rangkaian?

Pada rangkaian B3 dihubungkan ke input CLOCK. Saat B3 diputus, maka ketika Set dan Reset tidak aktif atau saat B0 dan B1 berlogika 1 akan terjadi kondisi Not Change karena pada rangkaian tidak dihubungkan ke CLOCK yang membuat J-K akan tetap pada kondisi sebelumnya.

3) Jelaskan apa yang dimaksud kondisi toggle, kondisi not change, dan kondisi terlarang pada Flip-Flop!

- Kondisi toggle merupakan kondisi yang komplemen/berlawanan dari kondisi sebelumnya tetapi tetap dalam keadaan stabil dan selalu berpindah.

- Kondisi not change merupaka kondisi pada flip flop yang mempertahankan kondisi sebelumnya atau tetap.

- Kondisi terlarang adalah kondisi pada rangkaian flip flop saat keluaran Q dan Q’ pada Reset dan Set bernilai 1 atau saat Set dan Reset keduanya aktif.

0 komentar:

Posting Komentar