PSPICE WINDOWS

A. TUJUAN (Daftar Isi)

1. Mempelajari dan mengetahui cara kerja PSPICE WINDOWS

2. Mengetahui identifikasi PSPICE WINDOWS

3. Menyimulasikan rangkaian pada PSPICE WINDOWS

B. ALAT DAN BAHAN (Daftar Isi)

1. Transistor JFET dan Transistor Unipolar

|

| transistor JFET |

Transistor FET (Field Effect Transistor), dalam hal ini JFET (Junction Field Effect Transistor) adalah transistor yang bekerja dengan memanfaatkan efek kejadian dalam medan listrik.Transistor FET mempunyai tiga elektroda, yaitu : Gate (G) atau pintu, Drain (D) atau cerat, dan Source (S) atau sumber. Ada dua jenis FET, yaitu type-N (kanal N) dan type-P (kanal P).Jika pada transistor bi-polar (Junction Transistor) jalan masukannya yaitu basis diberi tegangan muka maju terhadap emitor, maka pada JFET jalan masukannya (gate) diberi tegangan muka terbalik terhadap source.

2. Battery

Baterai berfungsi sebagai sumber energi listrik yang nanti dialirkan dalam rangkaian listrik.

3. Ground

C. DASAR TEORI (Daftar Isi)

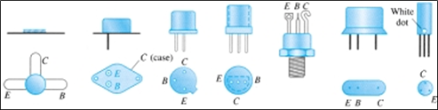

Setelah transistor dibuat dengan menggunakan salah satu teknik yang dijelaskan dalam Bab 12, timah, biasanya, emas, aluminium, atau nikel kemudian dipasang dan seluruh struktur dikemas dalam wadah seperti yang ditunjukkan pada Gambar 3.29. Perangkat dengan konstruksi tugas berat adalah perangkat berdaya tinggi, sedangkan perangkat dengan kaleng kecil (topi atas) atau bodi plastik adalah perangkat berdaya rendah hingga sedang.

Gambar 3.29 Various types of transistors:

(a) Courtesy General Electric Company;

(b) and (c) Courtesy of Motorola Inc.;

(d) Courtesy International Rectifier Corpo-ration

Jika memungkinkan, casing transistor akan memiliki beberapa tanda untuk menunjukkan kabel mana yang terhubung ke emitor, kolektor, atau basis transistor. Beberapa metode yang umum digunakan ditunjukkan pada Gambar 3.30.

Gambar 3.30 Transistor terminal identification

Konstruksi internal paket TO-92 di jalur Fairchild terlihat pada Gambar 3.31. Perhatikan ukuran yang sangat kecil dari perangkat semikonduktor sebenarnya. Ada kabel ikatan emas, bingkai tembaga, dan enkapsulasi epoksi.

Empat (quad) individu pnp transistor silikondapat ditempatkan dalam kemasan plastik dual-in-line 14-pin yang tampak pada Gambar 3.32a. Sambungan pin internal terlihat pada Gambar 3.32b. Seperti paket IC dioda, lekukan di permukaan atas menunjukkan pin nomor 1 dan 14.

Gambar 3.31 Internal construction of a Fairchild transistor in a TO-92 package

Karakteristik JFET n-channel dapat ditemukan dengan cara yang sama seperti digunakan untuk transistor bipolar. Rangkaian kurva untuk berbagai tingkatV. membutuhkan sapuan bersarang di bawah sapuan utama untuk tegangan drain-to-source.

Parameter Vto = - 3 mendefinisikan VGS = VP = - 3 V sebagai tegangan pinch-off—sesuatu untuk diperiksa ketika kita mendapatkan karakteristik kita. Memilih Analisis Pengaturan ikon (ingat bahwa garis biru horizontal di bagian atas), Sapu DC pertama kali diaktifkan dan kemudian diaktifkan untuk menghasilkan kotak dialog Sapu DC.Hasilnya adalah sekumpulan karakteristik yang muncul pada Gambar 5.47. Label yang tersisa ditambahkan menggunakan ikon ABC. Perhatikan bahwa tegangan pinch-off adalah 3 V, seperti yang diharapkan oleh parameter Vto. Itu nilai IDSS sangat dekat dengan 12 mA.

D. ESSAY (Daftar Isi)

JFET pada gambar 2.5 (a) memiliki VGS(off) = -4V dan IDSS = 12 mA. Tentukan nilai minimumdari tegangan VDD yang dapat menempatkan FET pada daerah arus konstan, jdari tegangan VDD yang dapat menempatkan FET pada daerah arus konstan, jika RDika RD= 560 Ω dan= 560 Ω danVGS = 0 !

Solusi :

Karena VGS(off) = -4 V, maka VP = 4V, yang merupakan juga nilai minimum dari VDS agar FETbekerja memiliki arus yang konstan.bekerja memiliki arus yang konstan

Dengan VGS = 0, maka arus konstannya adalah IDSS = 12 mA.arus konstannya adalah IDSS = 12 mA

Tegangan yang ada pada RD akan sama dengan

i.VRD= (12mA)(560Ω) = 6,7 V

Dengan demikian tegangan VDD harus sama dengan

ii.VDD = VDS + VRD = 4V + 6,7V = 10,7 V

E. PILIHAN GANDA (Daftar Isi)

- Lembaran data untuk JFET N-Channel MPF3821 menunjukkan nilai maksimum dari IGSS = -0,1nA pada 250C untuk VGS = -30V dan nilai maksimum dari IGSS = -100nA pada 1500C untuk VGS = -30V . Tentukan resistansi input minimum pada 250C

A. 300

B. 150

C. 200

D. 250

Solusi :

a. Tegangan Pinch-off adalah Tegangan pada saat arus berhenti bertambah (titik B). tegangan VGS(OFF) adalah Tegangan VGS yang menyebabkan arus drain menjadi nol.

b. Tegangan Pinch-off adalah Tegangan pada saat arus berjalan bertambah (titik B). tegangan VGS(OFF) adalah Tegangan VGS yang menyebabkan arus drain menjadi nol.

c. Tegangan Pinch-off adalah Tegangan pada saat arus berhenti bertambah (titik B). tegangan VGS(OFF) adalah Tegangan VGS yang menyebabkan arus drain menjadi 1.

d. Tegangan Pinch-off adalah Tegangan pada saat arus berjalan bertambah (titik B). tegangan VGS(OFF) adalah Tegangan VGS yang menyebabkan arus drain menjadi 1.

F. PROBLEM (Daftar Isi)

Tentukan wilayah operasi untuk JFET pada Gambar 5.49 jika VDSmax 25 V dan PDmax 120 mW.

Jawaban :

G. PERCOBAAN (Daftar Isi)

1. Prosedur Percobaan

· Siapkan dan jalankan aplikasi proteus

· Siapkan semua alat dan bahan

· Susun rangkaian pada papan rangkaian sesuai materi

· Sambungkan dan jalankan rangkaian

2. Rangkaian Simulasi

Pada rangkaian tersebut terlihat bawah tidak terdapat arus pada base transistor itu disebabkan karena pada base transistor tidak terdapat arus yang masuk sehingga transistor nya menjadi tidak on

H. VIDEO (Daftar Isi)

1. Video Materi

2. Video Rangkaian

0 komentar:

Posting Komentar